RAM

RAM

| ספרייה: | זיכרון |

| הוצג: | 2.0 בטא 1 |

| מראה: |

|

התנהגות

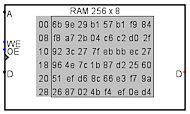

רכיב ה-RAM, בקלות הרכיב המורכב ביותר בספריות המובנות של Logisim, מאחסן עד 16,777,216 ערכים (המצוינים בתכונת Address Bit Width), שכל אחד מהם יכול לכלול עד 32 סיביות (מצוין ב- התכונה Data Bit Width). המעגל יכול לטעון ולאחסן ערכים ב-RAM. כמו כן, המשתמש יכול לשנות ערכים בודדים באופן אינטראקטיבי באמצעות הכלי Poke, או שהמשתמש יכול לשנות את כל התוכן באמצעות כלי התפריט.

ערכים נוכחיים מוצגים ברכיב. הכתובות המוצגות מופיעות באפור משמאל לתצוגה אֵזוֹר. בפנים, כל ערך רשום באמצעות הקסדצימלי. הערך בכתובת שנבחרה כעת יהיה מוצג בטקסט הפוך (לבן על שחור).

רכיב ה-RAM תומך בשלושה ממשקים שונים, בהתאם לתכונת Data Interface.

- יציאת טעינה/אחסון סינכרונית אחת (ברירת מחדל)

-

הרכיב כולל יציאה אחת בצד המזרחי שלו המשמשת הן לטעינה והן לאחסון נתונים. מה שהוא מבצע תלוי בקלט שכותרתו ld: 1 (או צף) מציין לטעון את הנתונים בכתובת המצוינת בצד המערבי של הרכיב, ו-0 מציין לאחסן את הנתונים שניתנו ב- נמל. כדי להעביר נתונים אל הרכיב ומחוצה לו, תצטרך להשתמש במאגר מבוקר רכיב, כפי שמוצג להלן.

- יציאת טעינה/אחסון אסינכרונית אחת

-

זה כמו לעיל, רק שאין שעון. הערך שנמצא באפיק הנתונים מאוחסן ב זיכרון בכל פעם שהקלט ld הוא 0. אם, בעוד שהקלט ld הוא 0, הכתובת או הנתונים שינויים, ואז מתרחשת חנות נוספת. אפשרות זו נועדה לקירוב יותר את הממשק של הרבה זיכרונות זמינים בגישה אקראית.

- הפרד יציאות עומס ואחסון

-

שתי יציאות נתונים מסופקות - אחת בצד המערבי לאחסון נתונים, ואחרת בצד המזרחי עבור טעינת נתונים. אפשרות זו מסירה את הצורך בטיפול ב-Contled Buffer וכך זה קורה קל יותר לשימוש.

-

סיכות

- A בקצה המערבי (קלט, רוחב סיביות תואם לתכונת כתובת Bit Width)

- בוחר לאילו מהערכים בזיכרון המעגל ניגש כעת.

- D בקצה המערבי (קלט, רוחב סיביות תואם לתכונה Data Bit Width)

- קלט זה קיים רק אם נבחרה "יציאות עומס ואחסון נפרדות" עבור ממשק הנתונים תְכוּנָה. כאשר מתבקשת חנות (באמצעות השעון המשתנה מ-0 ל-1 בזמן שsel וstr שניהם 1 או צפים), הערך שנמצא ביציאה זו מאוחסן בזיכרון כרגע כתובת שנבחרה.

- D בקצה המזרחי (קלט/פלט או פלט, רוחב סיביות תואם לתכונת Data Bit Width)

- אם sel ו-ld הם 1 או צפים, אזי רכיב ה-RAM פולט את הערך שנמצא בכתובת שנבחרה כעת ביציאה זו. אם יש יציאת עומס/חנות בודדת, הערך נקרא מהיציאה הזו מאוחסן בכל פעם שמתבקשת חנות.

- str בקצה הדרומי (קלט, רוחב סיביות 1)

- אחסן: קלט זה קיים רק אם נבחר "יציאות עומס ואחסון נפרדות" עבור הנתונים תכונת ממשק. כאשר הוא 1 או צף, דופק שעון יביא לאחסון הנתונים שנמצאו בקצה המערבי לזיכרון (בתנאי שהקלט sel הוא גם 1 או צף).

- sel בקצה הדרומי (קלט, רוחב סיביות 1)

- בחירת שבב: קלט זה מפעיל או משבית את כל מודול ה-RAM, בהתבסס על הערך 1/צף או 0. הקלט מיועד בעיקר למצבים שבהם יש לך מספר יחידות RAM, רק אחד מהם יהיה מופעל בכל עת.

- משולש בקצה הדרומי (קלט, רוחב סיביות 1)

- קלט שעון: זה חסר כאשר הערך של תכונת ממשק הנתונים הוא "אחד אסינכרוני load/store port." בנסיבות אחרות, כאשר ld הוא 0, והקלט הזה עולה מ-0 ל-1 (ו-sel הוא 1/undefined ו-clr הוא 0), אז הערך כרגע הכתובת שנבחרה משתנה לכל ערך שנמצא בפין D. כל עוד כניסת השעון נשאר 0 או 1, עם זאת, הערך D לא יישמר בזיכרון.

- ld בקצה הדרומי (קלט, רוחב סיביות 1)

- טעינה: בוחר אם ה-RAM צריך לפלוט (ב-D) את הערך בכתובת הנוכחית (A). התנהגות פלט זו מופעלת אם out הוא 1 או לא מוגדר; אם out הוא 0, אז שום ערך לא נדחף אל D - אבל אם יש משולב יציאת טעינה/חנות, חנויות יופעלו.

- clr בקצה הדרומי (קלט, רוחב סיביות 1)

- נקה: כאשר זה 1, כל הערכים בזיכרון מוצמדים ל-0, לא משנה מהן הכניסות האחרות.

תכונות

כאשר הרכיב נבחר או מתווסף, הספרות '0' עד '9' משנות את

כתובת Bit שלו תכונת Width

ו-Alt-0 עד Alt-9 משנים את תכונתData Bit Width

שלה.- כתובת ביט רוחב

- רוחב הסיביות של סיביות הכתובת. מספר הערכים המאוחסנים ב-RAM הוא 2addrBitWidth.

- רוחב סיביות נתונים

- רוחב הסיביות של כל ערך בודד בזיכרון.

- ממשק נתונים

- מגדיר אילו משלושת הממשקים משמשים לתקשורת נתונים לתוך ומחוצה לו רְכִיב.

התנהגות כלי לתקוע

ראה זיכרון חיטוט במדריך למשתמש.

התנהגות כלי טקסט

אף אחד.

התנהגות כלי תפריט

ראה תפריטים וקבצים קופצים במדריך למשתמש.